# Design Guideline for Microfluidic Device and Component Interfaces (Part 2)

Addressing: chip thicknesses and further miniaturization

#### **Editors:**

Henne van Heeren (enablingMNT), Dirk Verhoeven (Axxicon), Tim Atkins (Blacktrace/Dolomite), Alexios Tzannis (IMT Masken Und Teilungen), Holger Becker (MicroFluidic ChipShop), Wilfred Beusink (Micronit), Pu Chen (Stanford University)

With contributions / suggestions and support from persons from the following organisations:

APIX, Axxicon, Bronkhorst, CEA-Leti, CfBI, CMC Microsystems, Corsolution, Cytocentrics, Diagnostics Biosensors, DIBA, Dolomite, enablingMNT, EV Group, EVEON, Fluigent, Fraunhofer IOF, IHP, IMTag, IMTEK, Invenios, IPHT, IVAM, LioniX, Memsmart, Microfluidic ChipShop, Microfluidic Consortium, Micronit, MinacNed, NIST, Philips, PhoeniX, Qmicro, SCHOTT Technical Glass Solutions, Semi, SIMTech Microfluidics Foundry, Skalene, SLAC National Accelerator Lab, Sony DADC, Stanford University, Stiplastics, TNO, University College London, University Twente, and many others.

Comments, suggestions and questions regarding this document can be addressed to:

Henne van Heeren enablingMNT –Netherlandshenne@enablingMNT.com 0031 7863 00748

This work was supported by the Microfluidic Consortium and the MFManufacturing project, co-funded by grants from the UK, France and the Netherlands and the ENIAC / ECSEL Joint Undertaking.

Version 3.0, June 2017

DOI: 10.13140/RG.2.1.3318.9364

# Design for Microfluidic Device and Component Interface Guidelines, version 3.0

# **Contents**

| C                                           | ontents  |                                                         | 2    |  |  |  |

|---------------------------------------------|----------|---------------------------------------------------------|------|--|--|--|

| Ν                                           | layor ch | nanges in the White Paper 3.0 versus 2.0                | 3    |  |  |  |

| 2.                                          |          |                                                         |      |  |  |  |

| 3 Introduction to this white paper's topics |          |                                                         |      |  |  |  |

| 4                                           |          | Il chip thicknesses and their tolerances                |      |  |  |  |

|                                             | 4.1      | Glass wafers                                            | 7    |  |  |  |

|                                             | 4.2      | Polymer chip thickness                                  | 7    |  |  |  |

|                                             | 4.3      | Silicon wafers                                          | 8    |  |  |  |

|                                             | 4.4      | Microscope slides and cover slips                       | 8    |  |  |  |

|                                             | 4.5      | Most popular chip combinations                          | 9    |  |  |  |

| 5.                                          | Tow      | ards further miniaturization of chips and port pitches? | . 10 |  |  |  |

|                                             | 5.1      | Port pitches                                            | . 10 |  |  |  |

|                                             | 5.2      | Distance to the edge                                    | . 10 |  |  |  |

|                                             | 5.3      | Smaller chip sizes                                      | . 10 |  |  |  |

|                                             | 5.5      | Further miniaturization summarized                      | . 11 |  |  |  |

| 6                                           | And      | Finally                                                 | . 11 |  |  |  |

# Mayor changes in the White Paper 3.0 versus 2.0

Side connector transferred to Whitepaper "Design Guideline for Microfluidic Side Connect"

## 2. General introduction

#### Context

The goal of this document is to facilitate the process of designing new microfluidic sensors, actuators, connectors etc. by providing guidelines for the seamless integration with other microfluidic components and systems. This will overcome the challenge that the process of moving from a research prototype device to a production device takes too long and is too expensive.

#### Objectives of this paper

This White Paper is an attempt to improve the situation. It is made available for free to developers and researchers around the world who are contemplating the creation of prototype devices containing microfluidics. Its purpose is to present developers a standard by which they will improve the chances of their device will be accepted by the marker / fits to other products.

#### Positioning of this paper

This paper is "application agnostic" — it is be relevant to people working in: Diagnostics, High Throughput Screening, Sample Preparation, Genomics, PCR, Circulating Tumour Cells, Regenerative Medicine, Flow Chemistry, Environmental, Food and Homeland Security Sensing... and beyond!

This paper is also "materials and production technology agnostic" — we recognise that microfluidic devices can be realised in PDMS, PMMA, COC, Polycarbonate, Glass, Silicon, Metal and Paper as different players specialize in / have a preference for different materials. Furthermore this paper is "manufacturing process agnostic" — recognising again that processes can by company specific. Our vision is that newcomers to the microfluidics market — and companies that want to expand their product portfolio — will look at the relevant guidelines and design according to them. The process to create the products based on these designs will not be described or discussed in this paper. The paper especially addresses topics related to the issue of the microfluidic connections to microfluidic chips or substrates and the integration of microfluidic chips or substrates in components and systems.

Using these design guidelines will be helpful for both user and supplier by ensuring plug and play interconnections.

It is intended that this will be a "living document" updated regularly and the authors are keen on feedback regarding how the document might be improved.

Note: This document does not guarantee IP freedom to operate! There is a complex landscape of patents around microfluidics devices so it is up to you to check whether you need a licence!

The chosen approach concerning the guidelines towards connection/interfacing is to provide the minimum guidelines needed for interoperability, leaving open which materials to be used, what targeted applications and what connections types. We focused on keeping the guidelines simple, understandable by all and implementable by the product manufacturers as well as by the research labs. These guidelines are considered as a first essential step but certainly not an end point.

# 3 Introduction to this white paper's topics

This white paper is a follow up to our first white paper: Design Guideline for Microfluidic Device and Component Interfaces (part 1), Version 2.0, May 2016, DOI 10.13140/RG.2.1.1698.5206. That paper gave guidelines for:

- axes and reference point for chips,

- microfluidic ports,

- chip formats,

- exclusion zones for clamping or gluing chips,

- dimensions of sensor / actuator building blocks and

- operational conditions / application classes.

This white paper extends on this and is addressing: chip thicknesses and further miniaturization of chips and connectors.

# 4 Total chip thicknesses and their tolerances

Often microfluidic components are made by stacking individual chips; for instance channels in one chip covered by another chip which might have other features like sensing, optical access, connections etc. This section deals with total chip stack thicknesses, an important feature for the design of clamped microfluidic connectors, handling in automated equipment etc.

Major considerations for choosing a certain chip thickness include:

- Mechanical strength for automatic or manual manipulation and processing.

- Optical signal attenuation for fluorescence intensity, luminescent intensity, absorbance detection. (For instance for optical access one plate should be as thin as possible.)

- Need for fast heating up / cooling down (for instance for PCR).

- Cost of fabrication.

- Availability of substrates.

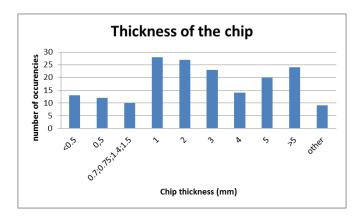

The discussion is complicated by the fact that there is no such thing as a standard substrate thickness as shown by the results of a recent survey:

Figure 1: Occurrences of chip thicknesses in microfluidics.

We will therefor approach the topic from two sides:

- 1) What substrates are available in the market; this argument is especially important for those working with glass.

- 2) What are the manufacturing constraints; this is for instance important for those that do injection moulding.

- 3) Constrains from the application; for instance the need for optical access.

Although people often talk about bottom and top plate, in practice this leads to confusion. In this paper we will use the term functional plate, where (most of) the microfluidic are and the cover plate. That does not imply that in the cover plate can't be microfluidic elements.

## 4.1 Glass wafers

It is advisable to choose from existing standard wafer thicknesses since they are readily available and cheaper since no polishing is required. Moreover, standard wafers have an excellent surface quality, e.g. surface roughness < 1 nm RMS, which in turn has a positive influence in manufacturability and yield. These wafers are available in a number of thicknesses. The company Schott for instance supplies 150 and 200 mm glass wafers with thicknesses between 0.03 mm and 1.1 mm. For D263¹ the standard available thicknesses are:

Table 1: Thicknesses of D263 wafers.

| nominal thickness<br>(mm) | thickness tolerance variation in lot (mm) | thickness variation referenced to net width (µm) |  |

|---------------------------|-------------------------------------------|--------------------------------------------------|--|

| 0.30                      | ± 0.020                                   | ≤ 20                                             |  |

| 0.40                      | ± 0.020                                   | ≤ 20                                             |  |

| 0.50                      | ± 0.030                                   | ≤ 20                                             |  |

| 0.55                      | ± 0.030                                   | ≤ 20                                             |  |

| 0.70                      | ± 0.050                                   | ≤ 30                                             |  |

| 0.90                      | ± 0.050                                   | ≤ 30                                             |  |

| 1.1                       | ± 0.050                                   | ≤ 40                                             |  |

For MEMpax<sup>2</sup> standard available thicknesses are: 0.2, 0.3, 0.4, 0.5, 0.7 mm with similar thickness tolerance and variation as D263<sup>3</sup>. The company Corning supplies glass wafers with thicknesses ranging from 0.4 mm to 1.1 mm, with thickness variation of 1-5%. The thickness standards of silicon wafers are also followed by producers of synthetic quartz wafers, e.g. Asahi Glass Corp and Shin-Etsu.

#### 4.2 Polymer chip thickness

Although other technologies are used, especially for low volume production and R&D, injection moulding is the most common technology to make polymer microfluidic devices. In moulded polymer devices you strive to have all structures in the moulded part. For good mould filling you want the part to be at least 1 mm thick; this thickness is enough for the most often used channel depths (100-300  $\mu$ m). Increasing thickness has a negative effect of cost. Several suppliers use 1.5 mm as a preferred choice, although microtiterplates are 2 mm thick.

The chips are covered in general with a thin foil. Preferable this foil is commercially available and of the same composition as the functional plate. Typical film thicknesses are between 100 and 250  $\mu$ m depending on the material. It is important to notice that the structures are usually at the bottom of the moulded part, allowing, if covered by the thin film, a short working distance on an inverted microscope (high NA) as well as a high thermal transmission for e.g. PCR applications.

\_

<sup>&</sup>lt;sup>1</sup> D 263® T eco is a clear borosilicate glass that has high chemical resistance and is produced by using a SCHOTT-specific down-draw method. It is available in a variety of thicknesses ranging from 0.03 mm to 1.1 mm.

<sup>&</sup>lt;sup>2</sup> A borosilicate glass that is manufactured with a fire-polished surface.

<sup>&</sup>lt;sup>3</sup> For instance 0,700mm (+/-0,025)

#### 4.3 Silicon wafers

The often used silicon wafers have standard thicknesses depending on their diameter as shown in the next table.

Table 2: Thicknesses of silicon wafers.

| Wafer size                                | Thickness (mm)  |

|-------------------------------------------|-----------------|

| 100 mm (usually referred to as "4 inch"). | 0.525 +/- 0.020 |

| 150 mm (usually referred to as "6 inch"). | 0.675 +/- 0.020 |

| 200 mm                                    | 0.725 +/- 0.020 |

| 300 mm                                    | 0.775 +/- 0.020 |

Silicon wafers of 100, 150 mm and 200 mm are often used to make sensors. 100 mm silicon wafers are slowly disappearing from the market, although still often used for niche applications and R&D.

# 4.4 Microscope slides and cover slips

Microscope slides are often used by researchers for creating microfluidic devices. There are a number of companies that also use this format. The slides are generally about 1 mm thick (according to the standard the thickness should be between 0.9 and 1.2 mm).

Cover slides<sup>4</sup> are much thinner; several versions are available with thicknesses ranging between 0. 085 and 0.64 mm. See for instance next table.

Table 3: Thickness of Schott D263M cover slides.

| Cover slip No. | Thickness (mm) |  |

|----------------|----------------|--|

| 0              | 0.085 to 0.13  |  |

| 1              | 0.13 to 0.16   |  |

| 1.5            | 0.16 to 0.19   |  |

| 2              | 0.19 to 0.23   |  |

| 3              | 0.25 to 0.35   |  |

| 4              | 0.43 to 0.64   |  |

<sup>&</sup>lt;sup>4</sup> University researchers use coverslip as a cover plate for microfluidic devices, as coverslips are more compatible than glass slides for microscope imaging especially for confocal imaging of cells.

# 4.5 Most popular chip combinations

As seen above, the variation of thicknesses is large. Not all combinations are practical and after discussions with several users and suppliers we came to the conclusion that the preferred thicknesses are:

- 0.16-0.24 mm (cover slips no 1.5 and 2 fall in this range and also the thinnest glass that is compatible with silicon direct-bonding: 0.2 mm)

- 0.67 0.73 mm (the often used 0.7 mm glass wafers and 150/200 mm silicon chips fall in this range)

- 1.5 mm for injection moulded devices

- 2 mm for higher pressure applications

In conclusion we recommend the following combinations for industrial designs:

Table 4: Preferred chip thicknesses and their combinations (thicknesses in mm).

|   | Functional         | Cover            | Material             | Operational classes <sup>5</sup> | Applications                                             |

|---|--------------------|------------------|----------------------|----------------------------------|----------------------------------------------------------|

|   | plate              | plate            |                      |                                  |                                                          |

|   | (mm)               | (mm)             |                      |                                  |                                                          |

| Α | 0.7 +/-            | 0.2 +/-          | Glass / glass or     | PT 2/50; PT 2/75; PT             | General microfluidic applications                        |

|   | 0.05               | 0.04             | glass / polymer      | 2/100                            | when optical access or fast heating / cooling is needed. |

| В | 0.7 +/-            | 0.7 +/-          | Glass / glass,       | PT 2/50; PT 2/75; PT             | General microfluidic applications                        |

|   | 0.05               | 0.3 <sup>6</sup> | glass / silicon      | 2/100                            | and microfluidic / silicon sensor                        |

|   |                    |                  |                      | PT 7/50; PT 7/75; PT             | combinations.                                            |

|   |                    |                  |                      | 7/100                            |                                                          |

| С | 1.05 +/-           | 0.2 +/-          | Glass / glass,       | PT 2/50                          | R&D applications when optical                            |

|   | 0.15               | 0.04             | glass / polymer      |                                  | access is needed, for instance                           |

|   |                    |                  | or polymer /         |                                  | using microscope slides and glass                        |

|   |                    |                  | polymer              |                                  | cover slides.                                            |

| D | 1.5 +/-            | 0.16 +/-         | Polymer /            | PT 2/50; PT 2/75; PT             | General microfluidic applications                        |

|   | 0.057              | 0.03             | polymer <sup>8</sup> | 2/100 <sup>9</sup>               | when optical access is needed.                           |

| E | 1.5 +/-            | 1.5 +/-          | Polymer /            | PT 2/50; PT 2/75; PT             | General microfluidic applications.                       |

|   | 0.05 <sup>10</sup> | 0.05             | polymer              | 2/100. <sup>11</sup>             |                                                          |

| F | 2 +/- 0.1          | 2 +/- 0.1        | Glass / glass        | PT 2/50; PT 2/75; PT             | High pressure applications.                              |

|   |                    |                  |                      | 2/100                            |                                                          |

|   |                    |                  |                      | PT 7/50; PT 7/75; PT             |                                                          |

|   |                    |                  |                      | 7/100                            |                                                          |

|   |                    |                  |                      | PT 30/50                         |                                                          |

$<sup>^5</sup>$  Operational classes as defined in the first white paper: for instance PT 2/75 means: pressure below 2 bar and temperature between 4 and 75  $^{\circ}$ C.

<sup>&</sup>lt;sup>6</sup> Be aware, the allowed range for the cover plate is larger than for the functional plate. We have taken a narrower range for the functional plate to ensure enough overlap between chip port and tube opening.

<sup>&</sup>lt;sup>7</sup> Depending on the design.

<sup>&</sup>lt;sup>8</sup> The most generally used polymer materials are: COC, PC, PMMA, COP or PS. Not all materials

<sup>&</sup>lt;sup>9</sup> Depending on the material.

<sup>&</sup>lt;sup>10</sup> Depending on the design.

<sup>&</sup>lt;sup>11</sup> Depending on the material:

# 5. Towards further miniaturization of chips and port pitches?

In some cases it might be advisable to use smaller chip; for instance for cost reasons or to minimize dead volume. This chapter shows a route towards smaller chips and their microfluidic connections.

# **5.1 Port pitches**

At this moment the situation is that we based ourselves on a grid of 1.5 mm. A port pitch of 3 mm is state of the art, but information from suppliers gave us confidence that 1.5 mm is realistic. If there is a need to go to even smaller pitches, 0.75 seems to be the obvious choice. Not only this offers a kind of backwards compatibility to the 1.5 grid, it also fits to the potential next step in Microtiterplate miniaturisation where a port pitch of 2.25 mm is foreseen. It must be said that 0.75 mm is not yet proven in technology and application.

# 5.2 Distance to the edge

Confirming to design constraints from the polymer manufacturers, a distance to the edge of 3 mm is chosen. Glass and silicon manufacturers with their smaller process tolerances are more tolerant to smaller distances. They ensured us that 1.5 mm is certainly possible and 0.75 mm might be realistic.

## **5.3** Smaller chip sizes

For chip manufacturing processes where the size of the chip is a substantial cost factor (glass processing, but especially silicon processing), the drive towards low cost processing is likely win from any drive to standard chipsizes. The reason is that cost sizes achieved by reducing chipsize will always be substantial more that cost savings due to using standardized chip sizes. Besides, silicon chips are never clamped but always connected to the motherboard by gluing, soldering, using glass frits and other technologies. The exception might be when the chip is packaged and not connected to a motherboard as a bare die. We will therefore discuss not so much chipsizes but package sizes. The package can also be used to fan out the ports. In that case, keeping a distance to the side of 3 mm and a port distance of 3 mm makes sense again, taking into account package technologies. The minimal size of the package will them be determinate by the number of ports.

#### 5.5 Further miniaturization summarized

Table 5: Port pitches and distance to the edge.

| Distance to side (mm)   Port pitch (mm) |      | Technology status                                       |  |

|-----------------------------------------|------|---------------------------------------------------------|--|

| 3                                       | 3    | State of the art, technology proven                     |  |

| 3                                       | 1.5  | State of the art, technology proven                     |  |

| 1.5                                     | 1.5  | Candidate for next step in roadmap, technology feasible |  |

| 3                                       | 0.75 | Likely not a standard                                   |  |

| 1.5                                     | 0.75 | Likely not a standard                                   |  |

| 0.75                                    | 0.75 | Candidate for future step in roadmap, technology        |  |

|                                         |      | challenging                                             |  |

It was decided that it makes sense to let the preferred chipsizes follow the port pitches. That still gives a high number of options. Experts believe that after the following options will be likely choices for the next generation.

Table 6: Preferred options for the next generation small microfluidic chips.

| Chip size (mm) | Port pitch (mm) | Distance to the edge (mm) | Maximum number of ports on the short side |

|----------------|-----------------|---------------------------|-------------------------------------------|

| 15*30          | 3               | 3                         | 4                                         |

| 15*15          | 3               | 3                         | 4                                         |

| 9 * 15         | 1.5             | 3                         | 3                                         |

| 9 * 9          | 1.5             | 3                         | 3                                         |

| 6 * 15         | 1.5             | 3                         | 1                                         |

| 6 * 9          | 1.5             | 3                         | 1                                         |

# 6 And Finally

As said, this White Paper is not a final document; it is just a reflection of the first discussions about microfluidic standards. Experienced engineers will find many other details to specify; organisations working on very lost cost disposables will stress the need for smaller chips and integration. Those interested in shorter times to market and higher reliability will stress the need for industry wide accepted validation test etc. etc.. Therefor we (and hopefully you too) will regard this as a living document. We are interested in your feedback and involvement to improve it!

We are grateful to the ENIAC /ECSEL project MicroFluidic Manufacturing and the Microfluidic Consortium that have supported this work. And thanks to many, many engineers and researchers who actively participated in the many discussions leading to this document.

To be continued